Rex 6000 PDA Pg 18

SOI Industry Consortium stalks the "green thing" Pg 6

Baker's Best Pg 16

Design Ideas Pg 39

Product Roundup Pg 46

Tales from the Cube: Finger on the trigger Pg 48

# PROVEN Critical Component Integrity DC-DC Converters 2V to 10,000 VDC Output

# Military Components

-55° to +85°C Operating Temp Military Environmental Screening Available 3.3 to 500 VDC Outputs M/MV Series Isolated - Regulated

# Wide Input Range

8 to 60 VDC Input 2 to 100 VDC Output Isolated-Regulated OR/IR/JR/KR Series 2-20 Watts

# 2 to 5000 VDC Outputs

Ultra Miniature Surface Mount and Thru Hole Single and Dual Isolated Outputs Military Upgrades Available AV/AV/SM/AVR Series

# 100 to 10,000 VDC Output Proportional Control Up to 10 Watts VV Series

# Programmable to 6000 VDC Output **HVP Series**

-40° and -55° to +85°C **Operating Temperatures** Wide Input Range 3.3 to 350 VDC outputs in 1/2 Brick and Ful Brick Military Upgrades Available LF/LM/FM Series

# HIGH POWER-Wide Input Range 2 to 350 VDC Output

Isolated to 300 Watts in 1/2 and Full Brick LP/HP/XP Series

# 36 to 170 VDC Inputs

Terminal Strips - Thru Hole 3.3 to 48 VDC Outputs Single and Dual Output LV/HV Series

Also Ac-DC single and 3 Phase. Power Factor Corrected, 3 Watts to 2000 Watts Models.

**Call Toll Free:** 800-431-1064

914-738-8225

# 5 to 500 VDC Output to 50 Watts Wide Input Range Isolated

Regulated QP Series

# www.picoelectronics.com

Complete Listing of Entire Product Line DC-DC Converters • AC-DC Inductors • Transformers E Mail: info@picoelectronics.com and Inductors.

Over 400,000 products in stock from more than 400 supplier partners.

An additional 1,000,000+ components can be sourced at digikey.com

The industry's broadest product selection available for immediate delivery

www.digikey.com 1.800.344.4539

# MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

# EDN<sub>8,20,09</sub> contents

# Transporting high-def video broadcasts: Are wireless networks up to the task?

High-resolution videostreaming support is supposedly a key justification for 802.11n versus its 802.11a and 802.11b/g predecessors. So why doesn't it deliver on its promises? by Brian Dipert, Senior Technical Editor

# Take advantage of open-source hardware

Basing your product on a reference design or demo board can speed time to market. by Gerald Coley, Texas Instruments

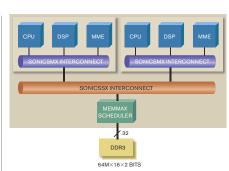

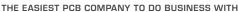

# Addressing interleaved multichannel memory challenges

Interleaving addresses in Multiple DRAM channels can greatly improve memory bandwidth, but it is not a trivial task. by Drew E Wingard, PhD, Sonics Inc.

- 10 Trigger, decode, and graphing packages simplify scopebased audio-bus debugging

- 11 Intel introduces speedy, inexpensive, 34-nm solidstate drives

- 11 Rotary-encoder IC meets all auto specs

- 12 Design and test combine to speed yield learning

- 12 Lithium-battery formulation suits medical applications

- 13 Western Digital packs 1 Tbyte into 2.5-in. disk

- 13 ASIC demultiplexes to multiple displays from one DisplayPort signal

- 14 Voices: Asset InterTech Inc's Tim Dehne: seeking growth in embedded instrumentation

# IGNIDEAS

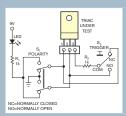

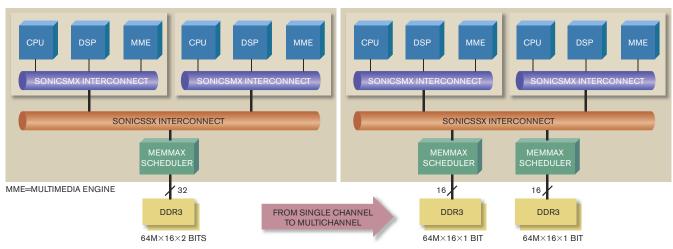

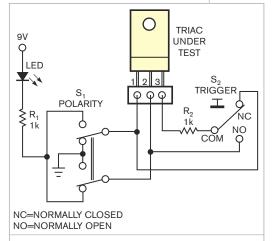

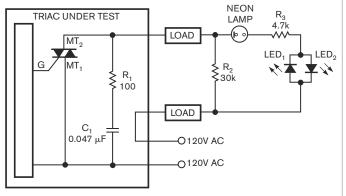

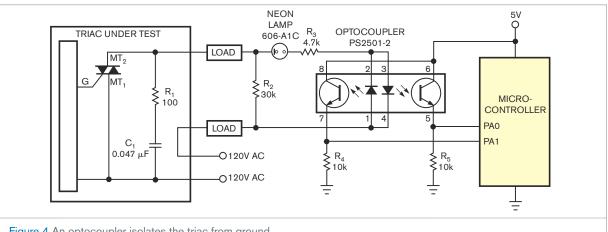

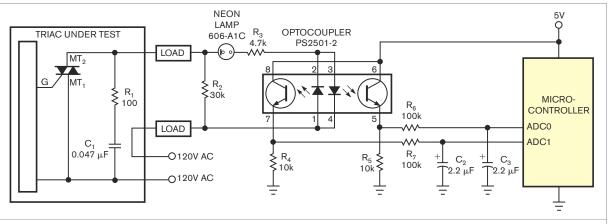

- 39 Triac tester allows for manual or automatic operation

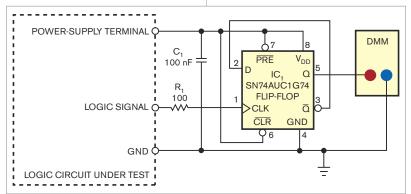

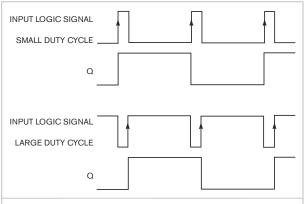

- 41 Handheld DMM copes with logic nanosecond-pulse-width waveforms

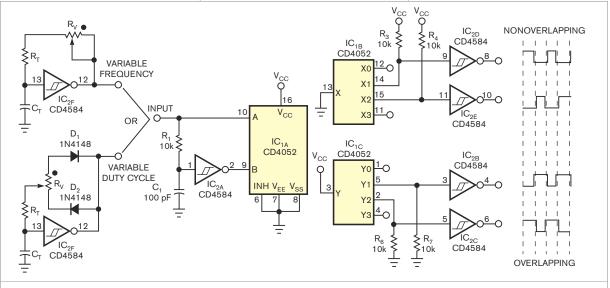

- 42 Build a simple complementary-bracket-pulse generator

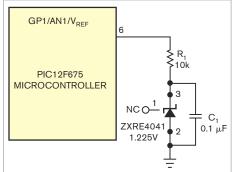

- 44 Power-miserly voltage reference needs just one pin

# The Newest Embedded Tools

# **New Products from:**

MPLAB PICkit 3 Debug Express www.mouser.com/ PICkit3debugexpress

Evaluation and Development Kits www.mouser.com/linx/a

# The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 390 leading suppliers.

a tti company

The Newest Products

For Your Newest Designs

(800) 346-6873

# contents 8,20,09

# **DEPARTMENTS & COLUMNS**

- 6 EDN.comment: SOI Industry Consortium stalks the "green thing"

- **Baker's Best:** One circuit provides system resolution and 12-bit accuracy

- 18 Prying Eyes: Rex 6000 PDA

- 46 **Product Roundup:** Cooling and Enclosures, Integrated Circuits

- 48 **Tales from the Cube:** Finger on the trigger

# **EDN** online contents

www.edn.com

# ONLINE ONLY

Check out these Web-exclusive articles:

# Designing a multicore + coprocessor security system

Network and communications processors are moving to heterogeneous processor configurations for efficiency, cost, and best-of-breed flexibility.

→www.edn.com/article/ CA6662010

# Choosing between an ARM7 and a Cortex-M3 processor

The Cortex-M3 offers compelling features over the ARM7, but the ARM7 currently has a larger manufacturers and tools ecosystem.

→ www.edn.com/article/

CA6673293

# FROM EDN'S BLOGS

# Top 16 CEO lies

From Leibson's Law, by Steve Leibson

It seems my peanut gallery's gotten all mumbly about Guy Kawasaki's 10 lies that engineers tell.

Perhaps they hit too close to home. So here's another of his lies list, 16 lies that CEOs tell and four things you wish they'd mouth instead.

Maybe this'll loosen your tongues.

→www.edn.com/090820toc1

# NSF research funds could benefit EDA -or not

From Practical Chip Design, by Ron Wilson Jeannette Wing, assistant director in charge of the National Science Foundation CISE (Directorate

for Computer and Information Science and Engineering), spoke to a packed luncheon audience on the subject of the NSF and EDA.

→www.edn.com/090820toc2

EDN® (ISSN#0012-7515), (GST#123397457) is published biweekly, 24 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer; Mark Finkelstein, President, Boston Division. Periodicals postage paid at Littleton, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2000 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year; Canada, \$229.99 one year (includes 7% GST, GST#123397457); Mexico, \$229.99 one year; air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Agreement No. 40685520. Return undeliverable Canadian addresses to: RCS International, Box 697 STN A, Windsor Ontario N9A 6N4. E-mail: Subsmail@ReedBusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 54, Number 16 (Printed in USA).

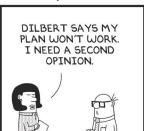

# Exceed 96% Efficiency

Save time, space, and energy with Gen2 Sup*IR*Buck<sup>™</sup> Integrated Voltage Regulators

IR3840 Efficiency vs. Load Current at 600kHz fs, 12Vin

|  | Part<br>Number | V <sub>IN</sub><br>Range<br>(V) | V <sub>оυт</sub><br>Range<br>(V) | lout<br>(A) | Switching<br>Frequency<br>(kHz) | Special<br>Features |

|--|----------------|---------------------------------|----------------------------------|-------------|---------------------------------|---------------------|

|  | IR3831MPbF     | 1.5 - 16                        | 0.7 -<br>0.9*V <sub>IN</sub>     | 8           | 250kHz -<br>1.5MHz              | DDR<br>Tracking     |

|  | IR3840MPbF     | 1.5 - 16                        | 0.7 -<br>0.9*V <sub>IN</sub>     | 12          | 250kHz -<br>1.5MHz              | SEQ input           |

|  | IR3841MPbF     | 1.5 - 16                        | 0.7 -<br>0.9*V <sub>IN</sub>     | 8           | 250kHz -<br>1.5MHz              | SEQ input           |

|  | IR3842MPbF     | 1.5 - 16                        | 0.7 -<br>0.9*V <sub>IN</sub>     |             | 250kHz -<br>1.5MHz              | SEQ input           |

For more information call 1.800.981.8699 or visit

International

Rectifier

THE POWER MANAGEMENT LEADER

# BY RON WILSON, EXECUTIVE EDITOR

# SOI Industry Consortium stalks the "green thing"

n these days, only government spending seems to drive the economy, and everyone is lining up to be under one of those government spigots. This situation is tricky for the semiconductor industry because it's hard to make a case for a fabless semi company as being essential to bailing out Morgan Stanley, rebuilding our highway infrastructure, or checking the spread of swine flu. However, there is one area—ergy saving—in which chips and foundries can claim some home turf.

Accordingly, just about half of new marketing programs have the word "green"—frequently capitalized—somewhere in the first paragraph of their promotional materials. Often, this approach is little more than spurious: an amplified echo of last year's key phrase, "low power." In some cases, though, the appeal to "greenness" makes sense, even without adding chlorophyll to the package epoxy.

One such situation is a new initiative—"Simply Greener"—by the SOI (silicon-on-insulator) Industry Consortium (www.soiconsortium. org). Part of the point is to hitch SOI to the green bandwagon. But there's content in there, too: One of the significant advantages of SOI is its ability to deliver a better speed-power product on a given project than a similar-geometry bulk-CMOS design. Some of the more prominent press coverage of SOI—AMD's travails and the heat problems with industry-leading game consoles, for example—may have obscured this fact. Nonetheless, it is true.

The SOI folks want to make clear the point that you can use that speedpower-product advantage to save significant power at the same speed. To

The consortium wants you to know that SOI brings built-in power savings, and it is mainstream.

underline that fact, a recent presentation gives examples of benchmark tests from ARM and IBM, which show side-by-side designs of blocks in SOI and in bulk CMOS. In ARM's case, a 45-nm-datapath design, the SOI version achieved an almost-threefold reduction in leakage and an approximately 20% reduction in dynamic power. IBM's example was more apples-to-oranges: a full-chip migration from 65-nm bulk CMOS to 45-

nm SOI, resulting in an approximately one-third reduction in power and a 50% speedup. In these instances, the choice of SOI instead of the bulk process appears to be making more difference than the use of aggressive power management.

The mechanism for the efficiency gain seems to be simple—probably simpler than it actually is. Because SOI builds its transistors directly over a buried insulating layer, the parasitic capacitances from the source, drain, and channel are much less than in a bulk wafer. By reducing these capacitances, a SOI transistor can operate with lower drive current and, hence, can be smaller; have a higher threshold voltage; or offer both features. Thus, both leakage and dynamic currents can be smaller at the same performance level.

A second point the SOI Consortium wants to emphasize is that SOI is available as an off-the-shelf foundry process, not just as a full-custom technology. "There's a wide range of regular users now," says Horacio Mendez, executive director of the consortium. "Almost everything IBM is building at 45 nm is in SOI, as are all of Freescale's latest networking chips. Casio is using the technology at extremely low power levels for watches, and some vendors are applying the technology in automotive applications." Foundry service is available from IBM and Chartered Semiconductor, among others.

SOI not only is a viable option for ordinary design teams but also has a road map, the organization claims. Processes are available in 65 and 45 nm, and both 32- and 22-nm processes are on the drawing boards. The main ideas the consortium wants you to know are that SOI brings built-in power savings, and it is mainstream. Those points deserve some discussion, even from teams that are tooling up to work on bulk CMOS.EDN

Contact me at ronald.wilson@reed business.com.

# Plug in to our Power Tools

Make better, faster power inductor choices with Coilcraft's powerful web tools.

Start with an IC, a converter topology, or a list of electrical and mechanical specs. In seconds you'll get a list of every Coilcraft part

that could work for you, complete with price information. A few more clicks gives you a detailed analysis of core and winding losses.

Check out our complete power designer's toolbox at www.coilcraft.com/powertools

# "I need to see the most signal detail."

Look no further.

InfiniiVision scopes are engineered for the best signal visibility.

# It's a bold claim — let us prove it to you.

Agilent engineered the custom MegaZoom III technology in our Agilent InfiniiVision scopes so you get the best possible signal visibility on every measurement you make.

- 1. **Fastest uncompromised update rate** shows you critical signal detail and gives you statistically valid measurement results in seconds.

- Industry's only hardware accelerated mixed signal oscilloscope gives you analog, logic, and protocol views.

- Customize your scope with software applications including mask testing, RS-232/UART, CAN/LIN and more.

100 MHz to 1 GHz MSO and DSO models

Take the 5-minute Scope Challenge online and register to win a free Agilent MS07104 scope. www.agilent.com/find/bestscopes

Prices in USD and subject to change without notice.

© Agilent Technologies, Inc. 2009

u.s. 1-800-829-4444 canada 1-877-894-4414

# PRESIDENT, BOSTON DIVISION, REED BUSINESS INFORMATION

${\it Mark Finkelstein}, \ {\it mark.finkelstein@reedbusiness.com}$

1-781-734-8431

## PUBLISHER, EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

### ASSOCIATE PUBLISHER, EDN WORLDWIDE

Judy Hayes, 1-925-736-7617; judy.hayes@reedbusiness.com

# VICE PRESIDENT, EDITORIAL DIRECTOR

Karen Field, 1-781-734-8188; kfield@reedbusiness.com

# EDITOR-IN-CHIEF, EDN WORLDWIDE

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

### **EXECUTIVE EDITOR**

Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

### MANAGING EDITOR

Amy Norcross

1-781-734-8436;

fax: 1-720-356-9161;

amy.norcross@reedbusiness.com

Contact for contributed technical articles

## SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

### ANALOG

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

# MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

# MICROPROCESSORS, DSPs, AND TOOLS

Robert Cravotta, Technical Editor 1-661-296-5096; fax: 1-303-265-3116; rcravotta@edn.com

# NEWS

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

# POWER SOURCES, ONLINE INITIATIVES Margery Conner, Technical Editor

1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

# DESIGN IDEAS EDITOR

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

# SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131; f.granville@reedbusiness.com

### **EDITORIAL/WEB PRODUCTION**

Diane Malone, Manager

1-781-734-8445; fax: 1-303-265-3024

Steve Mahoney,

Production/Editorial Coordinator

1-781-734-8442; fax: 1-303-265-3198

Melissa Annand,

Newsletter/Editorial Coordinator

1-781-734-8443; fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

## CONSULTING EDITOR

Jim Williams, Staff Scientist, Linear Technology

# **CONTRIBUTING TECHNICAL EDITORS**

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

### COLUMNISTS

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

## **PRODUCTION**

Dorothy Buchholz, Group Production Director 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

# EDN EUROPE

Graham Prophet, Editor, Reed Publishing The Quadrant, Sutton, Surrey SM2 5AS +44 118 935 1650; fax: +44 118 935 1670; gprophet@reedbusiness.com

# EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

# EDN CHINA

William Zhang,

Publisher and Editorial Director

wmzhang@idg-rbi.com.cn

Jeff Lu, Executive Editor

jefflu@rbichina.com.cn

# EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Address changes or subscription inquiries: phone 1-800-446-6551; fax: 1-303-470-4280; subsmail@reedbusiness.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# MAXIMUM)

# RELIABILITY

Mill-Max Mfg. Corp. spring-loaded connectors provide superior reliability under the most rigorous environmental conditions, offering:

- Continuous, low-noise electrical connections.

- Spike-free stability to 50G shock and 10G vibration.

- Continued high performance through 1,000,000+ cycles.

- Low- and high-profile surface-mount styles.

- 45 discrete designs for customer-specific assemblies.

- 6 families of single and double strip assemblies.

- The shortest production lead times in the industry.

**SLC Connector Assemblies**

Stay in contact with Mill-Max spring-loaded connectors.

To view our Design Guide, new product offerings and request a datasheet with free samples, visit

www.mill-max.com/EDN596

# Trigger, decode, and graphing packages simplify scope-based audio-bus debugging

he serial AudioBus triggering, decoding, and graphing packages for LeCroy Corp's WaveRunner Xi and WaveSurfer Xs oscilloscopes provide a complete set of tools for precise analysis and debugging of the I2S (inter-IC-sound) bus, a newly developed serial interface for digital-audio applications. The WaveRunner AudioBus decode capability includes a unique View Audio feature that converts the digitally encoded serialdata audio signal into an analog-waveform display. This capability provides an intuitive way to understand circuit problems that can cause clipping, glitches, and other anomalies in the audio circuit, as well as a way to see the effects of digitizing the audio signal before DSP has modified it. For conventional left/right-audio or home-cinema applications, which the TDM (time-division-multiplexed) audio buses enable, View Audio can simultaneously operate on as many as four audio channels.

AudioBus uses color-coded overlays on various sections of the decoded protocol data to produce an easily understood visual display. This exclusive feature is intuitive not only to experienced audio engineers but also to users who are new to I2S's LJ (left-justified), RJ (right-justified), and TDM audio-bus data formats. In addition, decoded information condenses or expands depending on the timebase/zoomratio setting, simplifying both routine verification and complex troubleshooting. You can choose to decode the data into hexadecimal, binary, decimal, or decibel formats.

You can also configure the AudioBus trigger to work with I<sup>2</sup>S's LJ or RJ variants, and you can apply conditional triggering to either left-or right-channel data. Unique triggers, such as

A WaveRunner Xi scope with the AudioBus TDG package provides a complete set of tools for analyzing and debugging the new serial I<sup>2</sup>S audio bus. In addition to enabling the scope to display the bus data as a color-coded analog waveform, the package transforms the scope into a protocol analyzer that can export the data as customizable spreadsheet files.

mute, clip, and glitch, help to isolate rare problems that you cannot easily detect by viewing only the decoded data. In addition, AudioBus turns the oscilloscope into a protocol analyzer with a customizable tabular display of protocol information that you can export as a Microsoft (www.microsoft.com) Excel file.

Access to the View Audio Waveform capability requires a WaveRunner scope and the \$1995 AudioBus TDG (trigger/decode/graph) package. The \$1345 AudioBus TD (trigger/decode) package works with both WaveRunner and WaveSurfer scopes.

-by Dan Strassberg

**▶LeCroy Corp**, www.lecroy.com.

# FEEDBACK LOOP

"What would those knotheads know about innovation? Some of my best work has begun with those little, fleeting moments when something you weren't even thinking about before suddenly gels in the mind and shapes up into something neither I nor anybody else anticipated or were even looking for."

—Consulting engineer and designer Thomas Fay, in *EDN*'s Feedback Loop, at www.edn. com/article/CA6666234. Add your comments.

# Intel introduces speedy, inexpensive, 34-nm solid-state drives

Ithough Intel and Micron's (www.micron.com) IM Flash Technologies partnership last November announced mass production of 34-nm lithographybased, 32-Gbit MLC (multilevel-cell) NAND-flash memories, Intel fabricated its first generation of MLC-derived solid-state drives, along with their SLC (single-level-cell) siblings, on 50-nm ICs. In July, Intel unveiled its second-generation 34-nm, MLC solid-state-drive products, although, at first glance, you might scratch your head at what the fuss is all about. Intel still calls the drives the X25-M family, and they come in the same 80- and 160-Gbyte capacities as their 50-nm predecessors, although they showcase a revised silver-case paint scheme.

Real-life performance improvements due to the 34-nmfabrication reduction, especially considering recent firmware updates of the 50-nm X25-M line, are also unclear. Intel says that the X25-M offers 25% lower latency and notably faster random-write operations than its 50-nm predecessor. The reduced latency offers quicker access to data, operating at 65-µsec read latency compared with approximately 4000 µsec for a hard-disk drive. Random-write performance has increased twofold for the 80-Gbyte version and 2.5-fold for the 160-Gbyte version. According to the company, the X25-M delivers as much as 6600 4-kbyte writeI/O operations/sec-8600 for the 160-Gbyte version—and as many as 35,000 read-I/O operations/sec.

Intel also admits that it does not expect substantial gains on application-based benchmarks versus its first-generation MLC solid-state drives. Conversely, targeted synthetic benchmarks and tests will reveal more noticeable differences. Lingering delays in 6-Gbps SATA (serialadvanced-technology-attachment) system-side support are likely a notable limiting factor in fully showcasing solid-state drives' speed strengths. However, Intel is passing along 34nm-process-lithography cost reductions to its customers. In July, the company was quoting channel prices for the 80- and 160-Gbyte X-25M of \$225 and \$440 (1000), respectively, a decrease from \$595 and \$945, respectively, at the 50nm-based product introduction a year ago. Intel is now shipping MLC solid-state drives in the 2.5-in, hard-disk-drive form factor, with 1.8-in. counterparts becoming available by the end of this guarter. Intel currently doesn't comment on the availability of 34-nm-derived SLC solid-state drives.

-by Brian Dipert **⊳Intel**, www.intel.com.

# The X25-M family 00 comes in 80- and 160-Gbyte capacities.

# **DILBERT By Scott Adams**

# **ROTARY-ENCODER** IC MEETS ALL AUTO **SPECS**

The AS5163 magnetic-rotary-encoder IC from austriamicrosystems satisfies the stringent automotive-ICprotection requirements in angle-sensing applications. The device provides overvoltage protection as high as 27V, and reverse-polarity protection withstands 18V reverse polarity at the supply pins. The device also has a short-circuit-monitoring function.

The AS5163 integrates all the functions of an analog or a digital magnetic-sensor rotary automotive temperatures.

Its designers envisage that applications for the chip will include throttlepedal sensing.

The AS5163 features a single-wire interface that you can configure as a 14-bit digital, 12-bit PWM (pulse-width-modulated), or ratiometric-analog output. You can also set it to cover any system-specific angle range by setting a start and end position of the rotational movement. The device operates at -40 to  $\pm$ 150°C, comes in a TSSOP-14 package, and requires a 5V supply.

-by Graham Prophet austriamicrosystems. www.austriamicro systems.com.

# Design and test combine to speed yield learning

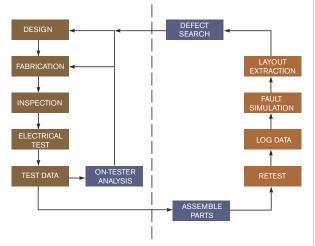

erigy has introduced its Yield Learning Solution, which integrates ontester, real-time capture and analysis of electrical failures on complex SOC (systemon-chip) devices. The product combines preanalysis modules on the Verigy V93000 SOC test platform, including a design-centric analysis and vi-

tools reduce the time required to diagnose problems. By seamlessly linking electrical test with physical-layout data, the tools allow fast localization of the root-cause physical defects.

Diagnosing problems in nanometer-level-device design and manufacture is becoming more challenging,

Verigy's on-tester analysis capabilities can shave weeks off the time it takes to make design revisions based on manufacturing test data, eliminating retest, fault-simulation, layout-extraction, and defect-search steps.

sualization tool set. The Yield Learning Solution comprises the V93000 scalable test platform plus the Triage Fault Locator and YieldVision software tool sets for failure data capture and yield analysis. Triage provides on-tester fault localization and includes an ontester sampling engine; Yield-Vision supports offline data analysis.

The scalable architecture of the V93000 allows for complete integration with the Yield Learning Solution. The Triage software's proprietary algorithms enable efficient data processing, and the YieldVision analysis and visualization

which makes it essential to close the loop between design, fabrication, and test, says Colin Ritchie, vice president of marketing for DFX (design-fortest/manufacture/yield) products at Verigy. Verigy's Yield Learning Solution addresses the design/fab matching that is essential for a successful business. He notes that design-for-manufacturability problems can result from lithography-unfriendly design or failure to adequately follow increasingly restrictive design rules. The inability to quickly isolate and fix such problems, he says, can lead to billions of dollars in lost annual revenue,

citing VLSI Research (www. vlsiresearch.com) figures.

Ritchie notes that traditional approaches to yield diagnosis can require many days to identify design problems that lead to yield loss; such iterative approaches often require retest of failed devices plus a sequence of fault simulation and layout extraction to physically locate faults. The process not only is time-consuming but also can generate terabytes of data. In contrast, says Ritchie, Verigy's on-tester approach generates only kilobytes of data and delivers results in minutes.

The Yield Learning Solution efficiently links test back into both design and the fab, providing logic bit maps for both stuck-at and difficult-to-detect timing faults in scan chains and logic. The Yield Learning Solution provides both the accuracy necessary for the lab and the high throughput necessary for production-critical for both new-product introduction and ongoing manufacturing monitoring. Ritchie says that Triage can perform on-tester localization of blocked scan chains and hold-time faults while performing on-tester characterization. YieldVision, he says, "speaks the language of the designer and the language of the fab," providing diagnosis at the wafer, die, and component levels. Ritchie cites customer results indicating a four-week acceleration in time to market, an increase in entitlement yield of as much as 6%, and a tenfold reduction in the number of waivers required to reach entitlement yield.

-by Rick Nelson

**Verigy**, www.verigy.com/go/yield.

# LITHIUM-BATTERY FORMULATION SUITS MEDICAL APPLICATIONS

**EaglePicher Medical Power** recently introduced a lithium-CFX (carbon-monofluoride)-battery chemistry, an enhancement of the company's proprietary CFX-battery technology. It results in a self-discharge rate of less than 1% per year at room temperature. Although lithium thionyl has a similar self-discharge rate, it increases rapidly with higher temperatures, making its use a liability in implantable medical devices, which must operate at 98.6°F.

The CFX formulation also offers energy density of 180 Whr/I-approximately 25% more than that of battery technologies that medical devices currently use. CFX lets battery-pack designers choose between a larger battery that runs for 25% longer and a 25% smaller one with an equivalent runtime.

The CFX formulation incorporates an end-oflife indicator to accurately predict battery depletion six months in advance, requiring fewer replacement surgeries for implantable medical devices. The indisharp falloff in voltage vet still maintains adequate voltage and power to operate. The new technology will be available in a number of configurations at powers of less than 350 mAhr to 10 Ahr.

by Margery ConnerEaglePicher, www.eagle picher.com.

# Western Digital packs 1 Tbyte into 2.5-in. disk

estern Digital recently broke its own record, becoming the first to shoehorn 1 Tbyte into a 2.5-in. hard-disk drive. This breakthrough comes on the heels of the company's becoming, in January, the first to ship a 2-Tbyte, 3.5-in. drive by squeezing four 500-Mbyte platters into the form factor. This approach was reminiscent of Hitachi's (www.hitachi.com) four-platter approach, landing that vendor in first place to cross the threshold for 1-Tbyte, 3.5-in. hard-disk-drive storage in early 2007. The company migrated to a three-platter configuration 18 months later.

Western Digital's drive, the WD Scorpio Blue, has a 3-Gbps SATA (serial-advancedtechnology-attachment) interface and an 8-Mbyte RAM cache. The MSRP (manufacturer's suggested retail price) is \$249.99; a 750-Gbyte version, the WD7500KEVT, sells for \$189.99. External USB (Universal Serial Bus)-interface variants are also available. MSRPs for the 1-Tbyte and 750-Gbyte versions of the My Passport Essential SE are \$299.99 and \$199.99, respectively. All these drives feature an atypical 5200rpm speed versus the more common 5400 rpm-whether for additional per-platter storage potential, to enhance the drives' power-consumption capabilities, or for other reasons.

Speaking of platters, the company accomplished its achievement by bumping the total per-drive platter count to three versus the more typical one- and two-platter specifi-

The 2.5-in., 1-Tbyte WD Scorpio Blue hard-disk drive has a 3-Gbps SATA interface and an 8-Mbyte RAM cache (a). The 1-Tbyte and 750-Gbyte versions of the My Passport Essential SE are external USB-interface versions of the Scorpio Blue (b).

cations. This augmentation increases drive height to 0.49 in. (12.5 mm), thereby making the drives unusable in some ultra-

thin-system designs, which rely on the more usual 0.374-in. (9.5-mm) thickness. As such, it's unclear how much if any per-platter areal-density leadership Western Digital has over competitors, such as Seagate (www.seagate.com).

Seagate is now promoting a 640-Gbyte, 2.5-in. hard-disk drive with an external USB interface. Presumably, the company based the product on asyet-unannounced, two-platter, single-drive technology, translating to 320 Gbytes per platter. Compare this data point to the 250- and 333-Gbyte/ platter specifications of Western Digital's latest offerings, and you can see how close the two companies are in this respect.

-by Brian Dipert >Western Digital Corp, www.wdc.com.

# ASIC DEMULTIPLEXES TO MULTIPLE DISPLAYS FROM ONE DISPLAYPORT SIGNAL

HDMI (high-definition multimedia interface) and DVI (digital-video interface) transmit video data as continuous bit streams, whereas DisplayPort transmits the data in packets and allows for asymmetric two-way transfers. If your application is simply connecting a graphics chip to a display, packetizing creates a lot of overhead for little real benefit. If you are driving multiple displays, however, there are some advantages to all that extra work. Chip designers and mechanical engineers who have to multitask need multiple displays. Both operating-system developers and the graphics-system designers have made provisions for this requirement. The question is how to get the data to the right display. One approach has been to use an additional display-driver card per monitor in the computer chassis. Another is with an external splitter box. Both of these approaches can cost hundreds of dollars and consume 100W or so. Another alternative is to go to USB (Universal Serial Bus)-display links, but that approach quickly runs into bandwidth problems.

IDT (Integrated Device Technology) may have a better idea with the VMM (virtual-machine-monitor) 1300 PanelPort ViewXpand chip. This device, powered by the DisplayPort cable at less than 1.5W, is basically a router for DisplayPort micropackets. The chip inspects incoming micropackets, sorts them based on the pixel addresses, modifies the address to correspond to the screen coordinates on the appropriate monitor, and routes each packet to that monitor. The chip works as a hub in a dongle, in which it can route packets to any of three output ports, or in a daisy-chain topology, in which you use only two outputs, and you can string together as many chips and monitors as your graphics bandwidth allows.

The chip can also function as a protocol converter, so, when it is in hub mode, you can drive legacy display interfaces on the chip outputs. The chip routes the Display-Port packets, so it requires no new driver software and is compatible with DisplayPort standards, including HDCP (high-bandwidth-digital-content protection) Version 1.3-a requirement for monitors that handle content-protected video.

At initialization, the chip uses identification cycles to figure out what monitors it will be driving and to map the viewing window onto the various monitors' screen coordinates, thereby setting up the routing table. The VMM 1300 is available for sampling, and production chips will become available this month.

-by Ron Wilson

Integrated Device Technology, www.idt.com.

# pulse

# **VOICES**

# Asset InterTech Inc's Tim Dehne: seeking growth in embedded instrumentation

im Dehne, until recently a longtime executive with National Instruments Inc, has joined the board of directors of Asset InterTech Inc, a supplier of boundary-scan and embedded-instrumentation tools. Over a career stretching more than 21 years at NI, Dehne led global marketing and R&D at the company, which reported \$824 million in revenues in 2008. During his tenure at NI, he held positions including vice president of strategic marketing and senior vice president of R&D. EDN recently spoke with Dehne. A portion of that interview follows. You can read the full interview at www.tmworld.com.

# This move represents a major change for you.

Yes, you could say that. I had been looking at a number of different options, but Asset InterTech presented a nice opportunity based on my experiences and relationship with Glenn [Woppman, Asset's chief executive officer and chairman]. It made sense to me, and I was happy to join the board.

What do you see as the similarities and differences in the directions of the two companies? National Instruments started out as a test company, but, as it grew, it's gone in lots of different directions, including control and design.

Growth potential is one of the things that got me excited when Glenn and I first started talking after I announced my departure from National Instruments. Asset's history is in boundary scan, which basically "niched out" as a market. Asset did very well

and is one of the leaders, but the space didn't grow as much as Asset and the other players in the marketplace hoped it would. But Asset is still fundamentally a hardware/software play, and that [approach] is very similar to National Instruments'.

But where the company is going is what got me excited. The semiconductor world is moving to many, many cores and even to multiple IP [intellectual-property] cores from multiple vendors. That world needs a kind of test strategy not only at the semiconductor level, where you figure out what's going on with the silicon and what may be causing some of the yield or performance issues, but also at the board level to monitor the interactions among all those different chips with all those multiple vendors' IP. Addressing these challenges involves structural test, which is different from what National Instruments does, but it seems to be an area of growth and an exciting technology develop-

ment. We feel that embedded instrumentation is an area in which the company can grow to quite a good size if we do things right.

# What are the prospects for mergers and acquisitions?

I'm not saying what Asset's plan is, but, in the design space, mergers and acquisitions happen all the time. They're not as frequent in the test area, but, of course, they occur there, too. But the most important thing now with Asset is to get the company growing organically with these new initiatives with the processor-controlled test and embedded instrumentation, so that's what we are going to focus on

# Do you plan to form partnerships with complementary vendors?

"Partnerships"-and I use that term looselytypically fall into three categories. There can be a sales/ distribution agreement, there can be just a marketing or message story, or there can be some in-depth joint development. The last type can be significant. Examples are the partnerships that NI had with Analog Devices [regarding NI's LabView graphical-development module for Analog Devices' Blackfin processors]

and Luminary Micro [regarding a LabView graphical-development module for ARM targets on a Luminary Micro evaluation board]. These partnerships involve developers' sitting down and co-developing and creating something new in the marketplace. With jointdevelopment efforts, generally there's money on the line; you are committing real resources, so you work harder to make those things work.

# What is your role as a board member-the traditional board of directors' governance role?

Certainly, anybody on the board has that role. But I'm a little bit different from the other board members, and I'm thankful to Glenn for recognizing the ways he could leverage my experience. When I started at National Instruments, the company employed 100 people, and I went up the marketing ranks for about a decade and then went into R&D for another decade. So given that experience base, Glenn and some of the other board members felt I could probably play a different role in addition to the corporate-governance role. I could also be a little bit more active in the marketing and R&D aspects.

-interview conducted and edited by Rick Nelson

# **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

# **Some Chips Have Moving Parts!**

Q. Is it true that over the years electrical devices have evolved to where they have no moving parts at all?

A. While it is true that any machinery becomes more reliable as the number of moving parts where friction can cause wear is reduced, there are actually integrated circuits (ICs) which only work because of moving parts on the surface of the chip.

These are known as Microelectromechanical Systems, or MEMS. They use standard IC process technology to make structures in metal, silicon and silica on the surface of a chip. Such structures may be designed to move and thus perform many useful functions.

Moving parts of such chips flex, but do not usually bear on other surfaces, so friction is not often a problem. They are usually made of silicon, which has very low mechanical hysteresis with deformation, and therefore great resistance to fatigue. Silicon does not change its properties or suffer damage even when flexed many trillions of times.

The first commercial MEMS devices with visibly moving parts were accelerometers. Electronic accelerometers once cost hundreds or thousands of dollars, today the least expensive cost only a dollar or two making it economical to use them in inexpensive gadgetry, air bag deployment (their first major application), joysticks for computer games, shock protection for disk drives and athletes ankles, keystone correction in projectors, orientation detection in hand-held monitors, and a thousand other uses.

Traditional gyroscopes rotate, but it's quite possible to make a gyroscope that vibrates rather than rotating; and this can easily be done in a MEMS structure. MEMS gyroscopes are used wherever rotation is measured; their low cost enables hitherto unaffordable applications such as optical image stabilization, safety controls in motor vehicles and short-range inertial navigation for GPS receivers when no satellite is visible.

MEMS structures allow the manufacture of high quality microphones on an IC chip. These are smaller, more cost-effective and reliable than any other microphone technology and are starting to replace the electret microphone in many applications.

The linked articles describe all these chips with moving parts, and their many uses, in much more detail.

> **To Learn More About MEMS Technologies**

http://designnews.hotims.com/23114-101

**James Bryant has** been a European **Applications Manager** with Analog Devices since 1982. He holds a degree in Physics and Philosophy from the University of Leeds. He is also C.Eng., Eur. Eng., MIEE, and an FBIS. In addition to his passion for engineering, James is a radio ham and holds the call sign G4CLF.

Have a question involving a perplexing or unusual analog problem? Submit your question to: rag@reedbusiness.com

For Analog Devices' Technical Support. Call 800-AnalogD

SPONSORED BY

# BY BONNIE BAKER

# One circuit provides system resolution and 12-bit accuracy

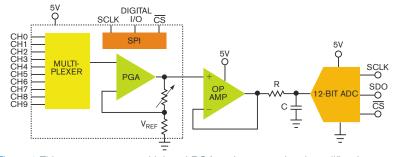

andheld meters, data loggers, and automotive and monitoring systems typically require a multiplexed system with the low-cost combination of high accuracy and high system resolution. A system that can handle this diversity requires a multiplexer, a gain cell, and an ADC. A feasible approach has a 10-channel PGA (programmable-gain amplifier) teaming up with a medium-speed, 12-bit SAR (successive-approximation-register) ADC (Figure 1). The single-supply,

10-channel PGA has a rail-to-rail I/O with a gain adjustment of 1 to 200V/V. The PGA's low-noise performance of  $12 \text{ nV/}\sqrt{\text{Hz}}$  at 10 kHz is appropriate for a 12-bit system.

The analog interface between these two devices includes an operational amplifier in a buffer configuration and an RC circuit. The 12-bit, capacitorbased SAR ADC has an inherent sample/hold function and requires the RC circuit, which facilitates the charging action of the ADC's input structure. The calculated value of the PGA noise, referred to the output, is equal to the PGA's noise density at 10 kHz  $(12 \text{ nV/}\sqrt{\text{Hz}})$  times the square root of the PGA's closed-loop bandwidth times the square root of  $\pi/2$ . The multiple of  $\sqrt{(\pi/2)}$  accounts for the noise in the frequency region beyond the PGA's bandwidth. You then multiply this number by the gain of the PGA. The following equation uses a PGA gain of 16V/V:  $PGA_{RMS-NOISE}$ =12 nV/  $\sqrt{\text{Hz}} \times \sqrt{(1.6 \text{ MHz} \times \pi/2)} \times 16 \text{V/V} =$  $304 \,\mu\text{V}$  rms. The ADC noise of 431  $\mu\text{V}$ rms from this converter is well below 1 LSB or 1.22 mV in this 5V system. The noise from the buffer amplifier, which is 39 µV rms, contributes little or no noise to this system.

The combined noise of the PGA, op amp, and ADC is 529  $\mu V$  rms, which is still less than 1 LSB of the 12-bit converter. You calculate this

value using a root-sum-square equation or the following equation: Noise referred to output= $\sqrt{(PGA_{RMS-NOISE}^2 + op amp_{RMS-NOISE}^2 + ADC_{RMS-NOISE}^2)}$ . The equivalent 12-bit accuracy of this system when the PGA is in a gain of 16V/V is 0.432 LSB: Noise referred to output×2<sup>N</sup>/FSR (full-scale range), where N is 12 and FSR is 5V/V. If you look at this system across the PGA's gain range of 1 to 200V/V, you find that the PGA dominates the noisecontribution portion in this circuit. Once the PGA gain exceeds approximately 125V/V, this system no longer matches the 12-bit-accuracy criterion. However, the system's referredto-input LSB voltage size becomes smaller (Figure 2). The trade-off for a smaller LSB is a decrease in the system's effective number of bits.

The system in **Figure 1** provides an adequate gain range for the PGA when 12-bit accuracy is required and an equally adequate gain range when good system resolution is required.**EDN**

Figure 1 This system uses a multiplexed PGA and an operational amplifier that drives a 12-bit converter.

Figure 2 The system accuracy is better than 0.01% with PGA gains of 1 to 125V/V. With PGA gains of 125 to 200V/V, the system accuracy is better than 0.02%.

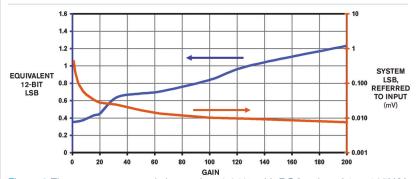

When it comes to creating your next embedded system, an important decision awaits you. Memory. Your design needs speed, reliability, performance and capacity to store the code and data your design demands. No problem. Numonyx has the broadest portfolio of parallel and serial NOR, NAND and phase change memory. And we offer extended temperature support with AEC-Q100 certification on many of our products and expanded design versatility with voltage support up to 5V. All designed to deliver a right-fit solution to help you shorten design cycles, reduce development costs and accelerate the roll-out of your next big idea. Find out how Numonyx memory matters for your next design.

| NUMUNTA FURIE " SERIAL FLASH MEMURT        |                |                  |  |  |  |  |  |

|--------------------------------------------|----------------|------------------|--|--|--|--|--|

| Product Family                             | Density Range  | Voltage/Solution |  |  |  |  |  |

| M25P (block erase)                         | 512 k - 128 Mb | 3V, single-I/O   |  |  |  |  |  |

| M25PX (4KB block erase)                    | 4 Mb - 64 Mb   | 3V, multi-I/O    |  |  |  |  |  |

| M25PE/M45PE (page erase)                   | 1 Mb - 16 Mb   | 3V               |  |  |  |  |  |

| NUMONYX® AXCELL™ PARALLEL NOR FLASH MEMORY |                |                  |  |  |  |  |  |

| Product Family                             | Density Range  | Voltage/Solution |  |  |  |  |  |

| M29W/FW (IFDFC command set)                | 4 Mh - 2 Gh*   | 3V page read†    |  |  |  |  |  |

64 Mb - 2 Gb\*

P30/33 (Intel-based command set, sync burst):

Visit www.Numonyx.com/Embedded for free access to the Numonyx Embedded Design Center.

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

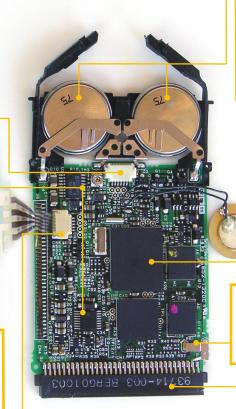

# Rex 6000 PDA

ranklin Electronic Publishers introduced the Rex electronic organizer at the 1997 Comdex show. The Rex was a Type II-compatible, 3.4×2.1×0.13-in., 1.4-oz PCMCIA, or PC-Card. The company later introduced a version with 512 kbytes of memory. Xircom bought the Rex line in 1999 for \$13.25 million. Intel acquired the Rex as part of its acquisition of Xircom, which was completed in March 2001. A month earlier, Xircom had introduced the Rex 6000, which Citizen Watch Company of Japan produced and marketed as the DataSlim-2. The organizer held phone numbers, a to-do list, an appointment calendar, a memo list, and several utilities, such as a calculator and some games. The Rex 6000 had 2 Mbytes of flash memory and 32 kbytes of RAM. It initially sold for \$150. Intel canceled the project shortly after its acquisition of Xircom.

Two 3V CR-2016 lithium batteries with 90-mAhr capacity power the PDA. The operating system shows a low-battery icon when power decreases to 2.86V and emits a warning at 2.82V.

The five hardware buttons connect through a six-circuit ribbon cable to a connector on the motherboard. The ribbon goes under the battery clip and snakes through a gap in front of the connector.

Analog chips include an Epson SCI7661 charge-pump dc/dc converter to make a negative bias for the LCD. A Texas Instruments quad, 10-bit, 85k-sample/sec TLV1544 ADC senses the touchscreen. Other analog chips include several linear regulators.

> The gray-scale, 240×120-pixel, 2.6-in.-diagonal LCD has no backlight. The display connects to a ribbon cable soldered to the motherboard. The row- and column-driver chips mount on the LCD glass.

The resistive touchscreen connects to the motherboard by a small, fivepin ribbon connector with only four used circuits. Icons on the bottom of the touchscreen provide seven soft buttons for the four primary PDA functions as well as a network download. a calculator, and a clock function.

A piezoelectric actuator lies on top of the chips to provide alarm and beeping sounds. Plastic tape over the back of the case ensures that the actuator and the battery do not short out.

> The 4.3-MHz Rex 6000 CPU is a Toshiba microprocessor that is compatible with the Zilog Z80. A separate 32.768-kHz watch crystal provides the real-time clock, two Fujitsu 29DL164BD-90 chips provide flash memory, and the fourth digital chip is an LCD controller.

A tab of metal forms a crude reset switch that users actuate through a small hole in the back of the case.

The PCMCIA form factor of the Rex 6000 allows you to synchronize it by sliding it into the PC-Card slot of a laptop computer. Alternative offerings are RS-232 and USB docks. The Rex does not use the PCMCIA bus to communicate; it uses the UART channel that is part of the PCMCIA standard. The USB cradle also emulates a serial UART.

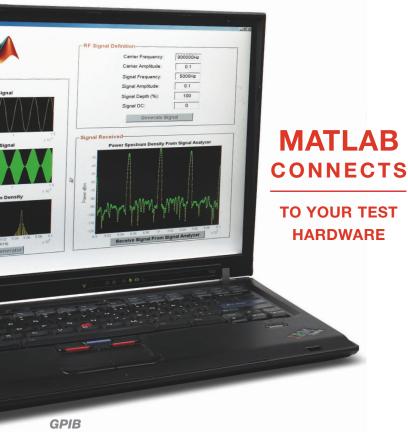

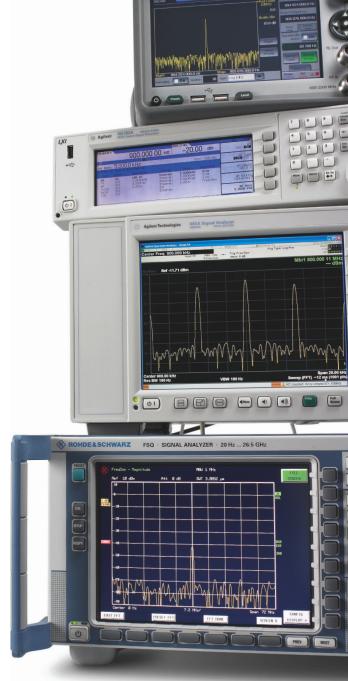

**Agilent**

**Tektronix**

**LeCroy**

Rohde & Schwarz

**National Instruments**

**Anritsu**

Keithley

Yokogawa

**Tabor**

**Pickering**

LXI

IVI

TCP/IP

**VISA**

**USB**

**UDP**

RS-232

Connect to your test equipment directly from MATLAB® using standard communication protocols and hundreds of available instrument drivers.

Analyze and visualize your test results using the full numerical and graphical power of MATLAB.

For more information on supported hardware, visit www.mathworks.com/connect

2009 The MathWorks, Inc.

MATLAB is a registered trademark of The MathWorks, Inc. Other product or brand names may be trademarks or registered trademarks of their respective holders.

any designers are familiar with open-source software, such as Linux, in which the source code is available to all. However, fewer are familiar with organizations offering open-source hardware. These organizations release free information, including schematics, BOM (bill-of-materials) information, and PCB (printed-circuit-board)-layout data, covering the overall hardware design. Designers with this information can build or add to a freely available design. In many cases, open-source software supports the original design, providing additional advantages. Some aspects of open-source hardware go beyond the sharing of the design itself. These aspects can save time and

# TAKE ON A REFERENCE DESIGN OR DEMO BOARD CAN SPEED TIME TO MARKET. ADVANTAGE OF OPEN-SOURCE LIANDON A REFERENCE DESIGN OR DEMO BOARD CAN SPEED TIME TO MARKET.

BY GERALD COLEY • TEXAS INSTRUMENTS

money for not only hardware developers but also PCB designers and fabricators, contract manufacturers, and even software developers.

You can license open-source projects from organizations such as Creative Commons, which offers the Attribution-ShareAlike licensing program. Creative Commons stipulates that a user must attribute the open-source work in the manner that the original designer specifies but not in a way that indicates that the original designer endorses the user's work. Likewise, if users provide that work as open-source hardware, releasing it back to the community for access by others, then they must provide that work under the same Attribution-ShareAlike licensing (Reference 1). Other licenses, such as the modified BSD (Berkeley Software Distribution),

allow for the assignment of copyrights and provide certain restrictions to the use of the hardware design (Reference 2). Be sure to read the license that comes with an open-source design before using it. If users are considering creating their own open-source design, they need to figure out which license works best for them.

You must consider several factors, including power, cost, and documentation, when selecting an open-source-hardware platform. Make sure that the license provides comprehensive, high-quality documentation, including schematics, BOM, and PCB data. The documentation must have the support of a large community of users, and it must align with your product's needs.

Some popular open-source-hardware platforms include Gumstix, Arduino, and

Figure 1 The BeagleBoard (bottom left) and the Overo expansion boards from Gumstix (top right) are examples of available open-source hardware.

the BeagleBoard (Figure 1). Gumstix uses an open-source-hardware model in posting the schematics and layouts of all the company's Overo-series expansion boards. Arduino employs a microcontroller as its hardware and has its own community of designers and hobbyists. Arduino's schematics come in Eagle and PDF (portable-document format), and the PCB information is in Eagle. The Creative Commons license covers licensing for the platform, and extensive libraries and software support are available. The BeagleBoard uses a Texas Instruments OMAP3530 (Reference 3). A large, Linux-based open-source-software community supports the BeagleBoard, and schematics are available in PDF and Cadence's OrCAD. The BOM is in Microsoft Excel, and PCB information is in Cadence's Allegro and Gerber files.

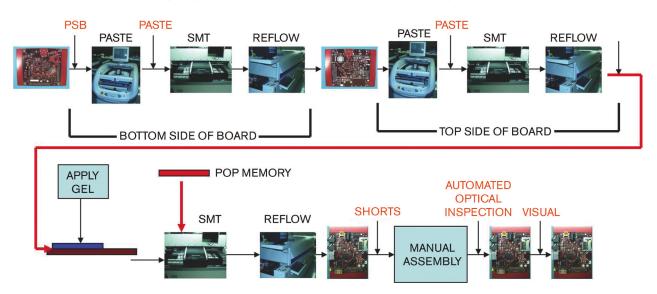

Due to its high technology level, the BeagleBoard presents some interesting challenges for users of the OMAP3530 device, but you can overcome the challenges by taking advantage of open-source hardware. The 515-pin OMAP3530 device uses 0.4-mm-pitch balls and supports POP (package-on-package) technology, which mounts the memory devices on top of the processor. This technology can create challenges, including schematic design and PCB layout, fabrication, and assembly.

# STREAMLINE THE DESIGN

You can reduce risk by basing designs

# AT A GLANCE

- Open-source hardware offers an advanced start on your design.

- Open-source software complements open-source hardware.

- Depense of the property of the

- You may want to share your improvements by making them open-source additions, as well.

on open-source hardware and taking advantage of a proven design that has operated successfully in the past. Thus, you can work from a known starting point and easily see what's there, what's missing, and what is unnecessary because you have access to both the finished hardware and the complete design. It also saves development time. Having access to the complete BOM with part numbers enables you to quickly adjust it. You can look for places to substitute your favorite capacitors and resistors and get access to the information on any unfamiliar parts. As long as the cost and specification of the part in use are on target, you should have no problem with using it. If you are unfamiliar with a part, however, you can improve the design by selecting a part better suited for your design's needs.

For instance, the OrCAD schematic

tool lets you quickly and easily add devices to the schematic. It takes advantage of the unused pins on the processor and even replaces devices on the opensource-hardware design. Creating components can take a lot of effort, so using those on the schematic saves time and reduces the risk of errors. Alternatively, you can use a PDF version of the hardware schematic to create schematics with your favorite tool. This approach can be an advantage because re-creating the design gives you more in-depth knowledge of how the design works and where problems might arise. The Beagle-Board's documentation includes a fairly detailed reference manual that can answer questions about the design. Users also can access the support community for additional help. Don't be afraid to ask for help; open-source hardware is all about learning from other people's mistakes.

Using the Allegro file format is the shortest path to completing a layout. You can import footprints from this database to your library, saving a significant amount of time. Because you already have a working board, you can use these footprints with confidence. If your board or prototype is similar to the BeagleBoard design and you need to add several components, you can simply do an ECO (engineering-change order), meaning that you use the current layout and add only key components so that you don't disturb the basic layout.

Figure 2 A board-assembly flow begins with a PCB and ends with a visual inspection of the work.

Manufactured and tested to MIL-PRF-27

www.picoelectronics.com

- Frequency range 20 Hz to 250 KHz

- Available from 100 milliwatts to 3 watts

- Impedance from 20 ohms to 100 K ohms

- Operating temperature -55°C to +130°C

- Low Profile from .24"ht.

- Thru-Hole available

Delivery-Stock to one week for sample quantities

Electronics,Inc. 143 Sparks Ave.. Pelham, N.Y. 10803 E Mail: info@picoelectronics.com

Allegro has a useful free viewer for reading design files. This viewer exposes the layer stacks and all of the PCB information, which provides a guide when designing the board on your own tool. In this way, you can see board routing, trace widths, and trace spacing. Another option is to convert the database to other tools using available and thirdparty tools. You must be careful not to lose design information when using this method, however. You can use Gerber files to double-check the information and as learning tools. These files are not user-friendly but can be helpful in creating your layout. The OMAP3530 device also includes a design-guideline application note to assist in layout.

# **GETTING UP TO SPEED**

Many new devices use more advanced technology, including blind vias, stacked vias, narrow traces, and via-in-pad technology, than the technology from your PCB supplier. Although the suppliers may be able to handle these advances, they may not have previously needed to provide it. If a user is comfortable with a PCB vendor because it's a known entity, though, it may be worth getting the vendor to the point at which it can handle the new needs. However, depending on your requirements and confidence level, you may be better off going to a vendor that has experience with the type of board you are working on. Using the available CAD data, the PCB vendor can get up to speed and prototype an initial board so that you are confident that the company can build it. If the vendor needs to adjust certain aspects of the design, it can modify the Gerber files for its normal processes.

Expected yield determines the cost of building boards. Building the board as it is gives vendors insight into yield. They can then prevent any problems that arise when building the new board. For example, if they have problems with via-

# FOR MORE INFORMATION

Arduino www.arduino.cc

BeagleBoard www.beagleboard.org

Berkelev Software Distribution www.bsd.org

Cadence www.cadence.com

**Creative Commons** http://creative commons.org

Gumstix www.gumstix.com

Realtime Technology www.realtimedsp. com.cn

Texas Instruments www.ti.com

in-pad technology, you should avoid using it in your design. The assembly house also may encounter problems in assembling your board. You can get the assembly house up to speed by using opensource hardware. Alternatively, you can use your own assembly house, if applicable, to build the entire board or a subset of the board.

In many cases, it can take several passes to work out the wrinkles in assembly. By using the open-source-hardware design and assembling as many boards as you need, you can solve any problems. It is better to work on these problems with a proven and tested board instead of your first prototype, on which it may be more difficult to find issues. The Beagle-Board also has a POP assembly guideline (Reference 4). As in the case of the PCB-layout guidelines, it also uses the BeagleBoard design (Figure 2).

There is always pressure to complete the hardware so that you can start the software verification. Basing your design on open-source hardware allows an early start on software development by using the available open-source-hardware boards to begin the development effort. Because open-source hardware typically also has a software component, the software team can jump-start its efforts by using the available code. This approach allows the hardware team to make sure it gets the design right on the first pass.

In addition, the software team may discover that it needs to change the hardware to improve performance or to add a feature. Making a lot of changes to the basic design quickly diminishes this advantage, however. Make sure that the basic design components, including the memory, power management, and key debugging peripherals, remain the same. Additionally, pay careful attention to the available software to see whether it offers the necessary applications or functions. Although software developers can write the software themselves, they typically would rather use the already-available software.

In summary, using the OrCAD schematic design tool or implementing your own version using open-source hardware reduces risk and saves development time. You then need to focus only on what to add or remove from the basic design to complete the final design. You can use the Allegro CAD files or Gerber files to provide a map with which

you can reuse whatever works correctly. Next, select a PCB vendor to accurately build the technology and save time and cost for the prototype run. This approach increases the chance of first-pass success and reduces the number of costly problems that would require re-spins and debugging during the prototype phase. Then, focus on getting the assembly house to build the open-sourcehardware board. Now that the hardware prototypes are ready to run software and you have tested the software from the open-source-hardware board, there is a much higher chance of success.

# **GIVING BACK**

Open-source hardware is about sharing work with others for everyone's benefit. It is acceptable if you never meant for the product to be open. You need not make your changes available to the community. In the spirit of open-source hardware, however, it's beneficial for all parties to provide upgrades and additions to the community whenever possible so that the next user can add other enhancements. When you add a function to hardware, it affects the software, which adds a reason to enhance and improve the overall performance of the software to take advantage of the new feature. As developers design products based on this design, another community member has perhaps added the function with the already-completed software work to help make it a better product.

In the future, more companies will offer varying levels of open-source hardware to their customers and the community at large, creating an environment in which developers spend most of their efforts on improving rather than re-creating the design. The community can benefit from this common goal, so keep your

- + Go to www.edn.com/090820df and click on Feedback Loop to post a comment on this article.

- + For more technical articles, go to www.edn.com/features.

eyes open for the next entrant in the world of open-source hardware.EDN

## REFERENCES

- "License Your Work," Creative Commons, http://creativecommons.org/ choose.

- Nelson, Russell, "The BSD License," Berkeley Software Distribution, Oct 31, 2006, www.opensource.org/licenses/ bsd-license.php.

- "OMAP3530 Applications Processor," Texas Instruments, www.ti.com/ omap3530-oshw.

- Gutierrez, Keith, and Gerald Coley "PCB Assembly Guidelines for 0.4mm Package-On-Package (PoP) Packages, Part II," Texas Instruments, April 2008, www.ti.com/litv/pdf/spraav2.

# **AUTHOR'S BIOGRAPHY**

Gerald Coley is a systems engineer at Texas Instruments, where he has worked for 13 years. Coley focuses on the OMAP processors and has designed more than 20 development boards, including the Beagle-Board.

HIGH-RESOLUTION VIDEO-STREAMING SUPPORT IS SUPPOSEDLY A KEY JUSTIFICATION FOR 802.11N VERSUS ITS 802.11A AND 802.11B/G PREDECESSORS. SO WHY DOESN'T IT DELIVER ON ITS PROMISES?

# TRANSPORTING HIGH-DEF VIDEO BROADCASTS:

BY BRIAN DIPERT • SENIOR TECHNICAL EDITOR

# AREWIRELESS NETWORKS UP TO THE TASK?

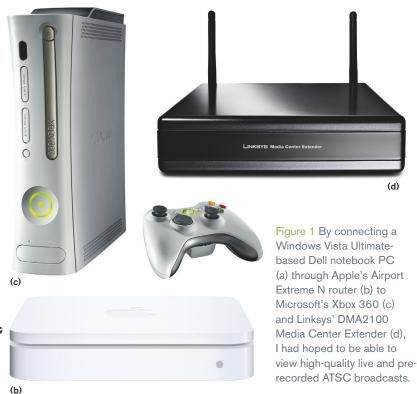

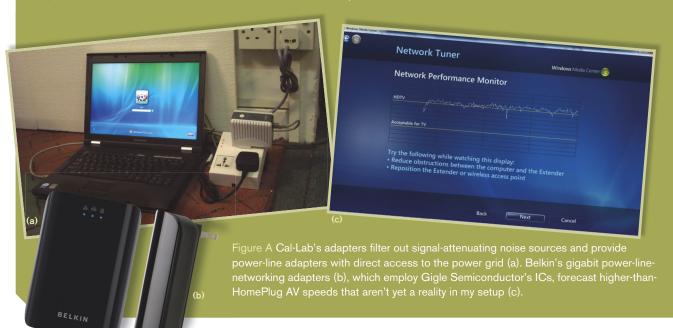

t all seemed so simple, at least at first glance. I have a Microsoft Windows Vista Ultimate-based notebook PC, a Dell XPS M1330. I have two Xbox 360s, one in the living room and the other in the bedroom (Figure 1). I have reasonably solid over-the-air television reception at my home office (Reference 1). I'm not using the XPS M1330 as a work PC because I've migrated to mostly Apple systems—in some cases running Windows XP virtualized. So I decided to convert the Dell PC to a PVR (personal video recorder), leveraging its built-in Media Center capabilities and streaming both live television and recordings to the game consoles acting as Media Center Extenders.

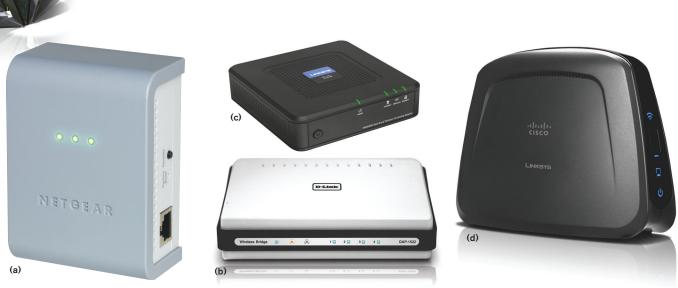

I don't have Category 5 Ethernet cable running to any of the three LAN nodes, so I at first tried connecting them to the router and each other using Netgear's XAV101 HomePlug AV power-line-networking adapters (Figure 2). This arrangement worked fairly well, especially once I stuck ac-noise filters on the refrigerator and furnace fans' power connections (see sidebar "Revisiting power line"). Erratic bandwidth still resulted in more frequent glitches in the playback than I preferred, sometimes but not always when ceiling or window fans or other potential power-grid noise sources were operating. With annoying regularity, one or both Extenders would also refuse to connect to the laptop until I power-cycled one, some, or all of the HomePlug AV adapters in use.

Finally, one day I threw up my hands in frustration, determined to find some alternative way—other than crawling under the house and punching holes in floors to string Category 5 cable—of interconnecting these nodes. Ideally, I hoped to completely dispense with power-line networking in my

LAN. (I was also using HomePlug AV to tether an Insteon home-automation controller to the router, thereby making the controller LAN- and WAN-accessible.) The XPS M1330 embeds a Broadcom 802.11n transceiver, my Apple router is 802.11n-capable, and 802.11n-based bridges and switches claim to allow legacy devices to leverage the IEEE's latest and greatest wireless-networking technology. Could 802.11n be my mentor to Media Center nirvana?

# THE DEVIL'S IN THE DETAILS

Before diving into the sordid step-by-step story, here is some important background information. First, the Broadcom Wi-Fi IC in the XPS M1330 is a BCM4328, which Dell refers to as the Wireless 1505 Module, and, in conjunction with its mated MIMO (multiple-input/multiple-output) antenna array, it is dual-stream- and dual-band-capable (Reference 2). Conversely, the XPS M1330's wired-Ethernet transceiver, a Broadcom 59XX-series IC, is not GbE (gigabit-Ethernet)-cognizant; it supports only 10- and

100-Mbps Ethernet. The XPS M1330, which is in the living room and less than 25 feet away from the same-room router, sources video streams whose parameters are also critical to this project's outcome. MPEG-2-based Media Center serves files that are on average larger and, therefore, have higher playback bit rates than those that more modern video codecs, such as MPEG-4 and VC-1, create. Microsoft offers four quality-versus-bit-rate settings, but they apply only to analog recordings.

With ATSC (Advanced Television Systems Committee) sources, Media Center does no re-encoding and otherwise does not alter the incoming MPEG-2 video and Dolby Digital audio data; Microsoft simply embeds it as is within the proprietary DVR-MS "wrapper" format. You should assume, therefore, that each live-TV or recording audio-plusvideo stream you want to route around your network is worst-case roughly 20 Mbps, accounting for DVR-MS overhead beyond the 19.2-Mbps ATSC bit rate. Media Center employs UDP (User Datagram Protocol) as the transport protocol, along with RTP (Real-Time Transport Protocol) for multimedia streaming and RTSP (Real-Time Streaming Protocol) for control functions.

In addition to Xbox 360s, the network nodes in my living room—12 feet away from the router—and in my bedroom also both include a Sony PlayStation 3. An Apple TV is in the living room, and the bedroom contains both a Roku Netflix Player and SoundBridge. I had been using a 10/100-Mbps Ethernet switch at each node to share the HomePlug AV connection among multiple pieces of gear because the HomePlug AV adapters aren't GbE-capable. (I have rarely had

# AT A GLANCE

- Power-line networking's longstanding shortcomings encouraged me to assess the validity of 802.11n's performance promises.

- Windows Media Center's reliance on MPEG-2 results in substantially higher bit rates than necessary with more modern video codecs.

- A single-channel, 5-GHz 802.11n topology couldn't deliver sufficient sustained bandwidth, due in part to my intra-LAN streaming scheme.

- A dual-channel approach improved the wireless network's peak speeds but also resulted in mysterious packet-dropping glitches.

- Gigle Semiconductor's Mediaxtream power-line-networking technology doesn't yet deliver on its GbE (gigabit-Ethernet) claims, at least in my setup.

more than one piece of gear simultaneously active at each node.)

Although all of these client devices support at least one IEEE 802.11 flavor, I wanted to simplify and optimize the performance of my migration from Home-Plug AV to 802.11n. I therefore planned to swap out each of the 10/100-Mbit wired-Ethernet switches for D-Link's DAP-1522, which combines a four-port GbE-capable switch and a dual-band, dual-stream 802.11n subsystem. The Insteon controller's single-client network node would require the use of only Linksys' simpler WGA600N or WET610N bridge devices.

# **BAND, ENCRYPTION CHOICES**

A bit of upfront research fortunately saved me some later hassles. An online review of the D-Link DAP-1522 revealed that the unit had subpar performance in 802.11n's 2.4-GHz band versus the 5-GHz alternative and that it performed worse with WEP (Wired Equivalent Privacy) and WPA (Wireless Protected Access)-plus-TKIP (Temporary Key Integrity Protocol) encryption than with the more modern WPA/AES (Advanced Encryption Standard) combination (Reference 3). My Apple 802.11ncognizant router also supports bonding together two wireless channels to boost the resultant bandwidth capability only in the 5-GHz ISM (industrial/scientific/medical) band. I was motivated to

(d)

lift the high-performance section of my Wi-Fi LAN above the already-cluttered 2.4-GHz spectrum that microwave ovens, wireless-surround-sound-speaker-transmitter/receiver combos, neighbors'

access-point signals, and other broadcasters populate. Also, in my diminutive open-air geodesic dome, the 2.4- versus 5-GHz-range discrepancy was not a practical concern.

The 5-GHz ISM band is comparatively crystal-clear in my rural locale. I therefore bound the Dell XPS M1330-to-router-to-D-Link DAP-1522 chain by means of a WPA-plus-AES-encrypt-

# REVISITING POWER LINE

I have so far been unable to dispense with HomePlug AV in my LAN, so I've spent some time determining whether I could improve the technology's robustness. In a sense, the power-line approach has an inherent advantage: The adapters can directly transfer data between them over the power grid with minimal router interaction. However, surge protectors and noise filters are equal parts curses and blessings for power-line networking. You can't plug an Ethernet-to-power-line adapter into them because the filter circuitry siphons off the networking data stream that's multiplexed on the ac-waveform carrier signal. Their omission from power-grid noise sources is equally debilitating to the power-line network, however.

Some signal attenuators are fairly obvious, notably motor-based products, such as stand-alone fans, heaters, air conditioners, refrigerators, vacuum cleaners, hair dryers, and the like. Other more obscure noise sources include the switching power supplies in ac/dc converters and battery chargers. Companies such as Cal-Lab sell specialized hardware that combines an unfiltered outlet for the power-line-networking adapter and a filtered connection, which also protects against lightning and other power surges, for noise-generating gear (Figure A). Similarly, Intellon recently sent me two PowerNet 200 HomePlug AV adapters that Monster Cable sells; the adapters integrate two filtered and protected power outlets.

Gigle Semiconductor recently partnered with Belkin

to unveil Belkin's F5D4076 gigabit power-line-networking adapters, which Gigle based on its GGL541 IC.

The GGL541 supports both HomePlug AV, which operates in the 2- to 28-MHz band, and Gigle's proprietary Mediaxtream technology, which uses the 50- to 300-MHz band. Like 5-GHz Wi-Fi versus 2.4-GHz 802.11, Mediaxtream's higher frequency delivers potentially higher performance. Indicative of this promise, the F5D4076 includes a 1-GbE (gigabit-Ethernet) transceiver, whereas consumer HomePlug AV adapters belie their "200-Mbps" marketing claims by embedding only 10/100-Mbps PHY (physical-layer) interfaces.

However, again as with 5-GHz versus 2.4-GHz wireless, Mediaxtream has notably shorter usable range than does HomePlug AV. The initial production firmware in the Belkin adapters selects either HomePlug AV or Mediaxtream mode, depending on the power-grid characteristics that the ICs' embedded DSPs determine at power-up. As you can see from the Network Performance Tuner plot, the adapters have selected HomePlug AV mode in my setup. In fact, they run slightly slower than my Netgear HomePlug AV-dedicated hardware, even at a two-node deficit. Gigle is working on firmware improvements, both to increase the number of supported nodes and to bond the HomePlug AV and Mediaxtream channels together rather than using a more elementary either-not-both approach.

Figure 2 Netgear's HomePlug AV adapters (a) were the initial means by which I connected various network nodes. Power-line networking's unreliability encouraged me to evaluate the 802.11n wireless alternative, enabled by D-Link's integrated switch plus access point (b), and two generations' worth of Linksys single-client bridges (c and d).

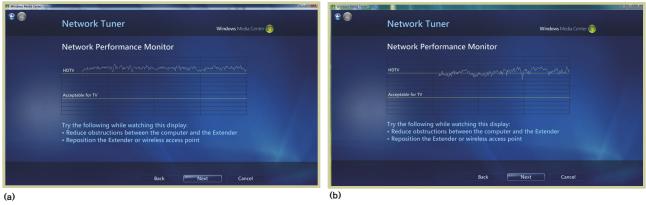

Figure 3 A HomePlug AV-only topology might be somewhat flaky (a), but it delivers faster streaming video than a single-channel, bonded 802.11n alternative (b).

ed 802.11n wireless spur running on Channel 149—that is, 5.745 GHz. I also tried other 5-GHz-band channels during later debugging. Initial streaming-attempt results were horrible: Windows Media Center's Network Performance Tuner utility measured best-case speeds of less than 8 Mbps. Nothing I tried improved the situation until I noticed that the laptop's Broadcom-sourced Windows Vista-driver suite carried a publication date of December 2006. Dell was still shipping it in the system that I had purchased in July 2008 (Reference 4)!

A visit to Dell's support Web site unearthed a slightly newer driver dated October 2007 available for downloading. At press time, Dell had made available no newer version. Installing the 2007-dated driver notably improved the

average speed of the wireless link but still not to a level at which it would reliably sustain streaming of a high-definition recording from the laptop to the game console (Figure 3). The Network Performance Tuner generates plots that define 22 Mbps as the requisite HDTV (high-definition-television)-bandwidth threshold and 8 Mbps as the acceptable-for-TV bandwidth. My 802.11n network's bandwidth capability also woefully undershot the 150-Mbps, single-stream and 300-Mbps, dual-stream claims of the technology's backers.

Pondering the problem uncovered a possible partial explanation, which several Wi-Fi-silicon-vendor representatives later confirmed. If my DSL (digital-subscriber-line) connection were capable of 20-Mbps sustained speeds

(it isn't), and if I were watching a 20-Mbps video from the Internet (I can't), the incoming data would enter the LAN through the router's wired-Ethernet WAN port, and it would then stream to the Xbox 360 over Wi-Fi. However, my video-streaming setup was intra-LAN in nature, and I was therefore using one Wi-Fi channel for two simultaneously transmitting, 20-Mbps data streams: one from the laptop to the router and another from the router to the game console. Even though that 802.11n channel had a 40-MHz-wide bonded-spectrum footprint, it was still insufficient for shouldering the entire bit load. Temporarily disabling the XPS M1330's 802.11n transceiver and instead connecting its Ethernet port to a Linksys WGA600N bridge yielded no improvement and